M of N element-by-element

|

|

| Vector | C | ST | |

| in the palette | on the schematic |

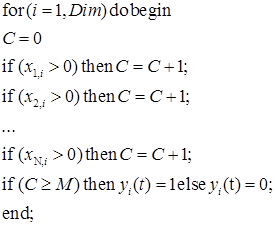

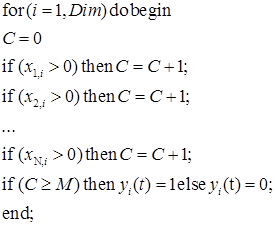

The block is analogous to the logic block M of N, is vectorized and performs the majorizing according to the following algorithm:

where: y(t), yi(t) are the output vector and the i-th element of the output vector. x1(t), x2(t), ... xN(t) - input vectors. M - parameter to compare with the total number of inputs N. x1,i - i-th element of the 1st input vector (etc.). The dimensions of input and output vectors must be equal. Dim - the number of signals in the input (and output) vectors.

where: y(t), yi(t) are the output vector and the i-th element of the output vector. x1(t), x2(t), ... xN(t) - input vectors. M - parameter to compare with the total number of inputs N. x1,i - i-th element of the 1st input vector (etc.). The dimensions of input and output vectors must be equal. Dim - the number of signals in the input (and output) vectors.

Thus, a logical 1 is formed at the output for each of i (for each of the signals in the input vectors) if C≥M (the number of non-zero i-th signals in the input vectors exceeds the parameter M). If C<M, the logical 0 is formed at the output (for each of the i-th elements).

Inputs

- u_n - the n-th inut port. The number of ports is configured in the block properties.

Outputs

- Y - operation result.

Properties

- Number of ports - number of input ports N.

- Number of True values for triggering - the number of M input signals equal to one, when reached, a logical one is formed at the output.

Parameters

none