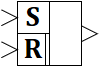

Reset-priority RS-trigger

|

|

| Vector | C | ST | |

| in the palette | on the schematic |

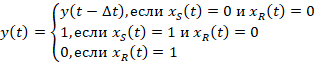

The block implements the reset-priority RS-trigger model, i.e. if the logical one level is present at the R and S inputs, then the output takes the logical zero value:

where y(t) is the output signal of the block, y(t – Δt) is the value of the output signal at the previous time step of integration, xS(t), xR(t) is the first and second input signals of the block (from English Set and Reset).

where y(t) is the output signal of the block, y(t – Δt) is the value of the output signal at the previous time step of integration, xS(t), xR(t) is the first and second input signals of the block (from English Set and Reset).

Inputs

- S – the input port for setting the trigger;

- R – the input port for resetting the trigger.

Outputs

- out – trigger output port;

- Yinv – the inverse output port (optionally added in the block properties).

Properties

- Initial conditions – initial values of the output logic signal;

- Add inverse output – indicates the presence of an inverse output.

Parameters

none